Xây dựng máy thu định vị vệ tinh trên nền công nghệ FPGA kết hợp ARM phục vụ các ứng dụng đặc biệt

478 lượt xemDOI:

https://doi.org/10.54939/1859-1043.j.mst.97.2024.177-180Từ khóa:

Định vị vệ tinh; FPGA; ARM; Zynq.Tóm tắt

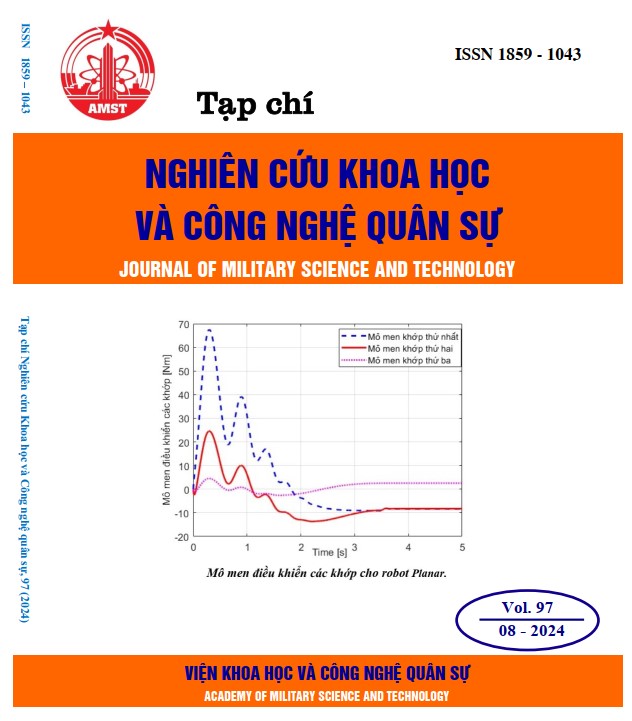

Bài báo này đề xuất một giải pháp xây dựng máy thu định vị vệ tinh trên nền công nghệ FPGA kết hợp ARM. Giải pháp được đề xuất dựa trên phương pháp và thuật toán kinh điển kết hợp với một số thuật toán bổ trợ tự phát triển, thực thi trên phần cứng tự thiết kế, chế tạo. Tín hiệu từ các quả vệ tinh thu được nhờ chip front-end được xử lý và đưa ra các kết quả định vị nhờ khối back-end được thực thi bởi phần cứng tự thiết kế, chế tạo với hạt nhân là chip Zynq. Khi thực hiện như vậy, máy thu định vị vệ tinh có tính linh hoạt hơn và quan trọng hơn cả là vượt qua được một số giới hạn mà nhà sản xuất các chip thu định vị thương mại đã khóa lại. Bên cạnh đó, kết quả nghiên cứu còn là tiền đề để thiết kế, chế tạo các chip thu định vị vệ tinh không chỉ cho những ứng dụng đặc biệt mà còn cho hệ thống định vị vệ tinh của riêng Việt Nam trong tương lai.

Tài liệu tham khảo

[1]. “European GNSS (Galileo) Open Service Signal In Space Interface Control Document (OS SIS ICD) Issue 1,” European Union/European GNSS Supervisory Authority (GSA), Tech. Rep., (2010).

[2]. “Fully integrated RF front-end receiver for GPS applications, STA5620 Data Sheet,” STMicroelectronics, (2008).

[3]. “Single-Chip Global Positioning System Receiver Front-End, MAX2742 Data Sheet,” Maxim, (2008).

[4]. G. Rivela, P. Scavini, D. Grasso, M. Castro, A. Calcagno, G. Avellone, A. Di Mauro, G. Cali, and S. Scaccianoce, “A low power RF front-end for L1/E1 GPS/Galileo and GLONASS signals in CMOS 65nm technology,” in Localization and GNSS (ICL-GNSS), 2011 International Conference on, pp. 7 –12, (2011). DOI: https://doi.org/10.1109/ICL-GNSS.2011.5955260

[5]. N. Qi, Y. Xu, B. Chi, Y. Xu, X. Yu, X. Zhang, and Z. Wang, “A dual-channel GPS/Compass/Galileo/GLONASS reconfigurable GNSS receiver in 65nm CMOS,” in Custom Integrated Circuits Conference (CICC), 2011 IEEE, pp. 1 –4, (2011). DOI: https://doi.org/10.1109/CICC.2011.6055350