Bộ trộn tần tuyến tính cao, băng thông rộng cho máy thu đổi tần trực tiếp trên công nghệ CMOS

574 lượt xemDOI:

https://doi.org/10.54939/1859-1043.j.mst.81.2022.44-52Từ khóa:

Máy thu đổi tần trực tiếp; Bộ trộn tần thụ động; Khuếch đại chuyển đổi dòng điện thành điện áp; Độ tuyến tính cao; Băng thông băng gốc rộng.Tóm tắt

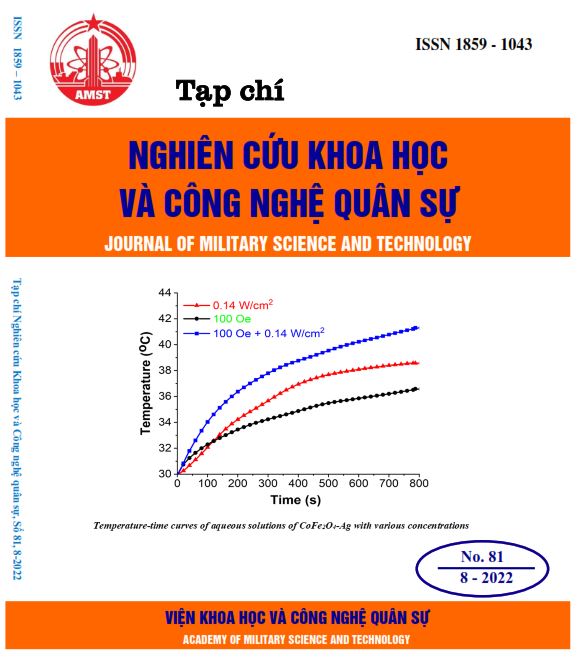

Bài báo này trình bày về bộ trộn tần xuống trong các máy thu đổi tần trực tiếp cho các hệ thống thông tin thế hệ mới như LTE và 5G có dải tần dưới 6 GHz. Một bộ trộn tần thụ động cân bằng kép được điều khiển bằng dòng điện kết hợp với tín hiệu dao động nội (LO) có độ đầy xung (duty-cycle) 25% được sử dụng để giảm tạp âm và cải thiện độ lợi chuyển đổi điện áp. Mạch khuếch đại chuyển đổi dòng điện thành điện áp (TIA) với kiến trúc dựa trên mạch đảo sử dụng lại dòng, tự phân áp được đề xuất để bộ trộn tần đạt được đồng thời độ tuyến tính cao và băng thông rộng. Bộ trộn tần được thiết kế trên công nghệ CMOS 28 nm. Kết quả mô phỏng sau layout cho thấy bộ trộn tần có khoảng thay đổi độ lợi chuyển đổi điện áp 0.45 dB mỗi 100 MHz trong băng thông băng gốc 580 MHz, hệ số tạp âm (NF) 9.2 dB, điểm chặn bậc hai đầu vào (IIP2) và điểm chặn bậc ba đầu vào (IIP3) lần lượt là 23.6 dBm và 61.5 dBm. Mạch tiêu thụ 40.1 mW công suất với điện áp nguồn cung cấp 0.9 V và có diện tích chiếm là 0.023 mm2.

Tài liệu tham khảo

[1]. 3GPP, 3rd-Generation Partnership Project; Technical Specification Group Radio Access Network; NR; User Equipment (UE) radio transmission and reception; Part1: Range 1 Standalone (Release 15), 3GPP TS 38.101 V15.6.0, June, (2019).

[2]. Technical Specification: 5G NR User Equipment (UE) Radio Transmission and Reception; Part 1: Range 1 Standalone, Release 15, V. 15.2.0, document 3GPP TS 38.101-1, Jul., (2018).

[3]. B. Razavi, RF Microelectronics, 2nd ed. Englewood Cliffs, NJ: Prentice-Hall, (2011).

[4]. Y. Gao, F. Huang, L. Wu and J. Cheng, “A low-power reconfigurable mixer for MB-OFDM UWB receivers,” in Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), pp. 97-100, (2009). DOI: https://doi.org/10.1109/PRIMEASIA.2009.5397437

[5]. J. Gou, X.-Y. Xu and X.-G. Huang, "Design of a Low-Voltage CMOS Mixer with Improved Linearity", in International Conference on IC Design and Technology (ICICDT), (2019). DOI: https://doi.org/10.1109/ICICDT.2019.8790840

[6]. A. Katarmal, A. Mecwan, and M. Patel, "RF CMOS Double Balanced Gilbert Cell Mixer for 5G Application", in 3rd International Conference on Signal Processing and Communication (ICPSC), (2021). DOI: https://doi.org/10.1109/ICSPC51351.2021.9451815

[7]. M. Kashani, M. Asghari, M. Yavari, and s. Mirabbasi, "A +7.6 dBm IIP3 2.4-GHz Double-Balanced Mixer with 10.5 dB NF in 65-nm CMOS", IEEE Transactions on Circuits and Systems-II: Express Briefs, vol. 64, no. 10, pp. 3214 – 3218, April, (2021). DOI: https://doi.org/10.1109/TCSII.2021.3072487

[8]. A. Nejdel, M. Abdulaziz, M. Törmänen, and H. Sjöland, “A positive feedback passive mixer-first receiver front-end,” in Proc. IEEE Radio Freq. Integr. Circuits Symp., pp. 79-82, Jun., (2015). DOI: https://doi.org/10.1109/RFIC.2015.7337709

[9]. S. Krishnamurthy and A. M. Niknejad, “Design and Analysis of Enhanced Mixer-First Receivers Achieving 40-dB/decade RF Selectivity,” IEEE Journal of Solid-State Circuits, vol. 55, no. 5, pp. 1165–1176, (2020). DOI: https://doi.org/10.1109/JSSC.2019.2956887

[10]. Qaiser Nehal, “Low power mixer-first receiver with second-order baseband filtering TIA,” in IEEE 63rd International Midwest Symposium on Circuits and Systems (MWSCAS), (2020). DOI: https://doi.org/10.1109/MWSCAS48704.2020.9184430

[11]. Hyungjoo Seo, and Jin Zhou, “A Passive-Mixer-First Acoustic-Filtering Superheterodyne RF Front-End,” IEEE Journal of Solid-State Circuits, vol. 56, no. 5, May, (2021). DOI: https://doi.org/10.1109/JSSC.2021.3067664

[12]. B. Razavi, “The Transimpedance Amplifier,” IEEE Solid-State Circuits Magazine, vol. 11, no. 1, Winter, (2019). DOI: https://doi.org/10.1109/MSSC.2018.2881860

[13]. N. Kim, V. Aparin, and L. E. Larson, "A resistively degenerated wide-band passive mixer with low noise figure and +60 dBm IIP2 in 0.l8 µm CMOS," IEEE Radio Frequency Integrated Circuits Syposium, pp.185-188, June, (2008).

[14]. D. Kaczman, M. Shah, M. Alam, M. Rachedine, D. Cashen, L. Han, and A. Raghavan, “A single-chip 10-Band WCDMA/HSPA 4-band GSM/EDGE SAW-less CMOS receiver with DigRF 3G interface and +90 dBm IIP2,” IEEE Journal of Solid-State Circuits, vol. 44, no. 3, pp. 718–739, Mar., (2009). DOI: https://doi.org/10.1109/JSSC.2009.2013762

[15]. A. Mirzaei, H. Darabi, J. Leete, and Y. Chang, “Analysis and optimization of direct-conversion receivers with 25% duty-cycle current-driven passive mixers,” IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, No. 9, pp. 2353–2366, Sep., (2010). DOI: https://doi.org/10.1109/TCSI.2010.2043014

[16]. P. K. Sharma and N. Nallam, “Linearity and NF tradeoff in input matched N-path mixer-first receivers with shunt-feedback TIAs,” in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), pp. 1–4, May, (2019). DOI: https://doi.org/10.1109/ISCAS.2019.8702176

[17]. J. Jiang, J. Kim, A. Karsilayan, and J. Silva-Martinez, “A 3–6-GHz Highly Linear I-Channel Receiver With Over +3.0-dBm In-Band P1dB and 200-MHz Baseband Bandwidth Suitable for 5G Wireless and Cognitive Radio Applications,” IEEE Transactions on Circuits and Systems–I: Regular Papers, vol. 66, no. 8, August, (2019). DOI: https://doi.org/10.1109/TCSI.2019.2909115

[18]. A. N. Bhat, R. van der Zee, S. Finocchiaro, F. Dantoni, and B. Nauta, “A baseband-matching-resistor noise-canceling receiver architecture to increase in-band linearity achieving 175 MHz TIA bandwidth with a 3-stage inverter-only OpAmp,” in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Boston, MA, USA, pp. 155-158, Jun., (2019). DOI: https://doi.org/10.1109/RFIC.2019.8701843

[19]. A. Martin: “Cadence Design Environment”, New Mexico State University, Oct., (2002).